Evolución y progreso del CPOoptoelectrónicotecnología de co-envasado

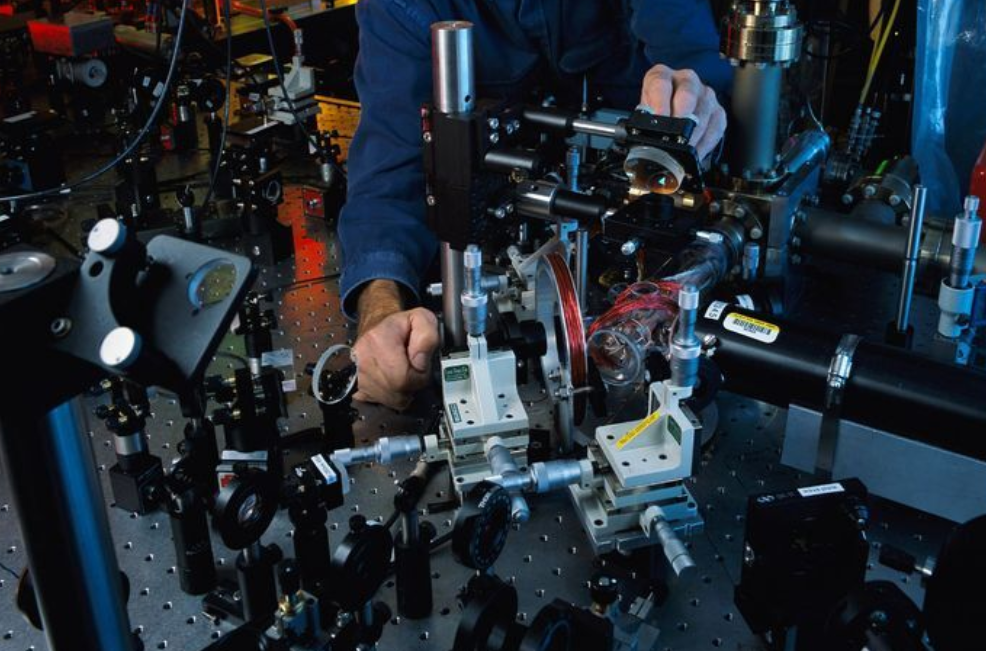

El co-empaquetado optoelectrónico no es una tecnología nueva, su desarrollo se remonta a la década de 1960, pero en este momento, el co-empaquetado fotoeléctrico es solo un paquete simple dedispositivos optoelectrónicosjuntos. En la década de 1990, con el auge de lamódulo de comunicación ópticaEn la industria, el coenvasado fotoeléctrico comenzó a surgir. Con el auge de la alta potencia de procesamiento y la alta demanda de ancho de banda este año, el coenvasado fotoeléctrico y su tecnología relacionada han vuelto a recibir mucha atención.

En el desarrollo de la tecnología, cada etapa también tiene diferentes formas, desde 2.5D CPO correspondiente a una demanda de 20/50Tb/s, hasta 2.5D Chiplet CPO correspondiente a una demanda de 50/100Tb/s, y finalmente realizar 3D CPO correspondiente a una tasa de 100Tb/s.

Los paquetes CPO 2.5D incluyenmódulo ópticoEl chip de conmutación de red (RC) se integra en el mismo sustrato para acortar la distancia de línea y aumentar la densidad de E/S. El CPO 3D conecta directamente el CI óptico a la capa intermedia para lograr una interconexión con un paso de E/S inferior a 50 µm. El objetivo de esta evolución es muy claro: reducir al máximo la distancia entre el módulo de conversión fotoeléctrica y el chip de conmutación de red.

Actualmente, el CPO se encuentra en sus inicios y aún presenta problemas como bajo rendimiento y altos costos de mantenimiento. Además, pocos fabricantes en el mercado pueden ofrecer productos CPO completos. Solo Broadcom, Marvell, Intel y algunas otras empresas ofrecen soluciones totalmente propietarias en el mercado.

Marvell presentó el año pasado un conmutador con tecnología CPO 2.5D mediante el proceso VIA-LAST. Tras procesar el chip óptico de silicio, el TSV se procesa con la capacidad de procesamiento de OSAT, y posteriormente se le añade el chip eléctrico flip-chip. Dieciséis módulos ópticos y el chip de conmutación Marvell Teralynx7 se interconectan en la placa de circuito impreso (PCB) para formar un conmutador que alcanza una velocidad de conmutación de 12,8 Tbps.

En la OFC de este año, Broadcom y Marvell también demostraron la última generación de chips de conmutación de 51,2 Tbps utilizando tecnología de empaquetado conjunto optoelectrónico.

Gracias a los detalles técnicos de la última generación de CPO de Broadcom, el encapsulado CPO 3D, gracias a la mejora del proceso, logra una mayor densidad de E/S, un consumo de energía de CPO de 5,5 W/800 Gbps y una excelente relación eficiencia energética. Al mismo tiempo, Broadcom también está avanzando hacia una única ola de CPO de 200 Gbps y 102,4 Tb.

Cisco también ha incrementado su inversión en tecnología CPO y realizó una demostración de producto CPO en la OFC de este año, mostrando su acumulación y aplicación de tecnología CPO en un multiplexor/demultiplexor más integrado. Cisco anunció que realizará una implementación piloto de CPO en switches de 51,2 TB, seguida de una adopción a gran escala en ciclos de switch de 102,4 TB.

Intel ha introducido desde hace tiempo conmutadores basados en CPO y en los últimos años ha seguido trabajando con Ayar Labs para explorar soluciones de interconexión de señales de mayor ancho de banda empaquetadas conjuntamente, allanando el camino para la producción en masa de dispositivos de interconexión óptica y empaquetado conjunto optoelectrónico.

Aunque los módulos enchufables siguen siendo la opción preferida, la mejora general en la eficiencia energética que aportan los CPO ha atraído a cada vez más fabricantes. Según LightCounting, los envíos de CPO comenzarán a aumentar significativamente a partir de los puertos de 800G y 1,6T, comenzarán a comercializarse gradualmente entre 2024 y 2025 y alcanzarán un volumen considerable entre 2026 y 2027. Al mismo tiempo, CIR prevé que los ingresos del mercado de los paquetes fotoeléctricos totales alcancen los 5400 millones de dólares en 2027.

A principios de este año, TSMC anunció que se uniría a Broadcom, Nvidia y otros grandes clientes para desarrollar conjuntamente tecnología de fotónica de silicio, componentes ópticos de empaquetado común CPO y otros productos nuevos, tecnología de proceso de 45 nm a 7 nm, y dijo que el segundo semestre del próximo año más rápido comenzó a cumplir con el pedido grande, alrededor de 2025 para alcanzar la etapa de volumen.

Como campo tecnológico interdisciplinario que abarca dispositivos fotónicos, circuitos integrados, encapsulado, modelado y simulación, la tecnología CPO refleja los cambios introducidos por la fusión optoelectrónica, y los cambios en la transmisión de datos son, sin duda, revolucionarios. Si bien la aplicación de CPO solo se observará en grandes centros de datos durante mucho tiempo, con la mayor expansión de la potencia de procesamiento y los altos requisitos de ancho de banda, la tecnología de cosellado fotoeléctrico CPO se ha convertido en un nuevo campo de batalla.

Se puede observar que los fabricantes que trabajan en CPO generalmente creen que 2025 será un nodo clave, que además es un nodo con una tasa de intercambio de 102,4 Tbps, y que las desventajas de los módulos enchufables se intensificarán. Si bien las aplicaciones de CPO pueden llegar con lentitud, el empaquetado conjunto optoelectrónico es, sin duda, la única manera de lograr redes de alta velocidad, gran ancho de banda y bajo consumo.

Hora de publicación: 02-abr-2024